# A 3D Integration Testing Vehicle with TSV Interconnects

Tiwei Wei<sup>1</sup>, Qian Wang<sup>1</sup>, Ziyu Liu<sup>1</sup>, Yinan Li<sup>3</sup>, Dejun Wang<sup>3</sup>, Tao Wang<sup>1</sup>, Jian Cai<sup>1,2,\*</sup>

<sup>1</sup>Institute of Microelectronics, Tsinghua University, Beijing 100084, P. R. China

<sup>2</sup>Tsinghua National Laboratory for Information Science and Technology, Beijing 100084, P. R. China

<sup>3</sup>Faculty of Electronic information and Electrical Engineering, Dalian University of Technology, Dalian 116024, P. R. China

\*Email: jamescai@tsinghua.edu.cn

#### Abstract

3D integration is one of the potential solutions for extending Moore's momentum in the next decennium. Through silicon via (TSV) is a key interconnect technology for future's higher performance and system integration with vertical stacked chips in package, which can achieve smaller interconnection delay, heterogeneous technologies integration and potentially lower cost and reduce time-to-market.

In this paper, a testing vehicle of 3D stacking dies with TSVs as the major interconnect was designed. A dummy die with  $5\mu m$  diameter TSVs was fabricated and assembled on a silicon interposer, which has TSVs as well. The dummy die/chip was bonded on the interposer through Cu-Sn-Cu bonding at  $280\,^{\circ}\text{C}$ ,and then, the bonded module was assembled on designed testing board.

### Introduction

**TSV** technology fabrication and micro-bump interconnection between stacked dies are recognized as the core technologies of 3D integration. Lots of research works focusing on the fabrication and applications of difference size have been published from TSMC(Taiwan), TSVs Samsung(Korea), Elpida(Japan), CEA-IMEC(Europe). Leti(France), ITRI(Taiwan, China)<sup>[1]</sup> and many other research institutions all around the world.

However, there are still many challenges when facing fine pad pitch (50  $\mu$ m) and small diameter(<10 $\mu$ m) TSV with high aspect ratio, such as wafer thinning and handling, alignment for warped wafers<sup>[2]</sup>, dishing and uniformity, bottom up electroplating, the performance of insulating liner , assembly and interconnection with thin die. When the TSV diameter and depth becoming smaller, the problems mentioned above will be more and more evident. Via diameters smaller than 5 $\mu$ m are very difficult to be filled with electroplated copper<sup>[3]</sup>. Thin wafer handling is also the cornerstones of 3D stacked IC manufacturing, the quality of temporary bonding process becomes particularly important as the wafer thinned to 30 $\mu$ m and below. When the wafer thickness becomes thinner, the warpage will be more serious because of the stresses. Moreover, it is very challenge to align the warped wafers.

This paper focuses on the design and fabrication of a 3D integration testing vehicle, which includes design of 3D integration testing vehicle with 5 $\mu$ m TSVs, fabrication of test chip with 5 $\mu$ m TSVs and key technologies like via formation, copper electroplating, temporary bonding process, wafer thinning and polishing, alignment for warped wafers etc, fabrication of 40 $\mu$ m Si interposer, and assembly process.

# **Design of 3D Integration Testing Vehicle**

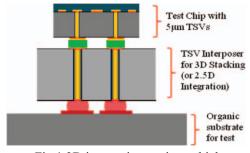

Fig.1 3D integration testing vehicle

Fig.1 shows the designed 3D packaging illustration enabled with small TSV (5 $\mu$ m) chip, TSV interposer chip and organic substrate.

As shown in the structure, the test chip with  $5\mu m$  TSVs was bonded on the interposer through Cu-Sn-Cu bonding, and the size of Cu/Sn microbump is  $60\mu m$  x  $60\mu m$ , with  $300\mu m$  pad pitch. Microbump layout was designed as mirror symmetrical with that of  $5\mu m$  TSV chip. The size of test chip with  $5\mu m$  TSVs is 6mm x 5mm, and the size of interposer with  $40\mu m$  TSVs is 7mm x 6mm.

And then, the bonded module was assembled on a designed BT substrate with dimension of 8.5mm x7.5mm through solder ball. Pad size for solder ball placing is  $100\mu m$  x  $100\mu m$ , pad size of surrounding is  $300\mu m$  x  $300\mu m$  with a pad pitch of  $500\mu m$ .

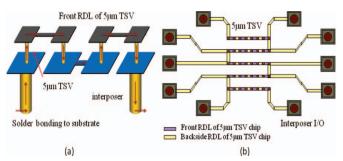

Fig.2 Daisy chain model (a) 3D view of TSV daisy chain model(b) Plane view of daisy chain

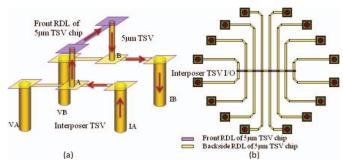

The designed daisy chain and Kelvin structure testing patterns are shown in Fig.2 and Fig.3. For the test chip with  $5\mu m$  TSVs, the diameter of TSV is  $5\mu m$ , and the chip thickness is  $25\mu m$  which has the aspect ratio of 5:1. Daisy chain structure for successful interconnect verification and Kelvin structure for electrical resistance measurement were designed.

Fig.3 Kelvin structure model (a) 3D view of TSV Kelvin structure model(b) Plane view of Kelvin structure

## Fabrication of Test Chip with 5µm TSVs

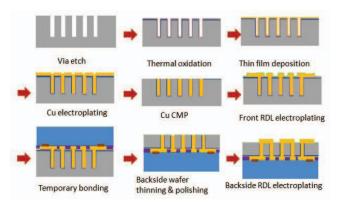

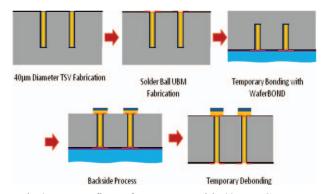

The dummy chip with  $5\mu m$  TSVs was fabricated in-house. Fig.4 presents the fabrication process of  $5\mu m$  TSV. The key processes of  $5\mu m$  diameter and high aspect ratio TSV fabrication are TSV etching, lining and via filling, optimized temporary bonding/ debonding, wafer handling.

Fig.4 Process flow of test chip with 5µm TSVs

### (A) Via filling of 5µm TSV

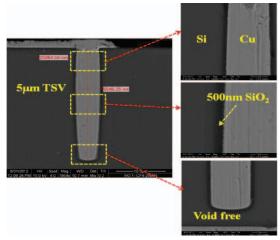

Photoresist was applied by lithography as mask of via formation. Deep Reactive Ion Etching (DRIE) process was used to form  $5\mu m$  diameter blind via, with the height of  $25\mu m$ . Bosch process was adopted with a STS DRIE etcher. After photoresist stripped, 500nm SiO $_2$  was formed through thermal oxidation, which was used as the insulating layer of  $5\mu m$  TSV. And then, barrier and seed layers with 200nm TiW/500nm Cu were sputtered.

Based on the uniform and continuous seed layer inside  $5\mu m$  diameter vias, robust copper electroplating process for  $5\mu m$  TSVs with high aspect ratio was realized.

The  $5\mu m$  TSV filling process was set up to adopt bottom-up Cu electroplating mechanism using electroplating chemicals from Shanghai Sinyang Semiconductor Materials Co., Ltd.

Current density is an important affecting factor in copper electroplating. Samples under different current densities were discussed in this paper. Low current density of 0.01ASD was used to fill the 5 $\mu$ m TSV for 16 hours with high aspect ratio up to 7:1, but it will take a lot of time. Voids at the bottom of the 5 $\mu$ m TSV were found as the current density was 0.1ASD. Finally, high current density of 0.25ASD was adopted as the

optimized plating parameters of  $5\mu m$  TSV Cu filling. The electroplating parameters of  $5\mu m$  TSV are shown in Table.1.

Table.1 Optimized plating parameters of 5µm TSV Cu filling

| Condition | Current<br>density | Electroplating<br>time | Results |

|-----------|--------------------|------------------------|---------|

| 1         | 0.01ASD            | 16hour                 |         |

| 2         | 0.1ASD             | 3hour                  |         |

| 3         | 0.25ASD            | 25min                  |         |

Fig.5 presents a cross-sectional view of bottom-up electroplated TSV. From the SEM images, the insulating layer/ barrier and seed layers can be seen clearly, and via filling is void free.

Fig.5 SEM images of 5µm TSV with upside pad

Subsequent copper chemical mechanical polishing (CMP) process was applied to remove Cu overburden on wafer surface, which could ensure copper planarization for wafer thinning and handling. According to the Cu CMP parameters reported in other paper<sup>[4]</sup>, less overburden on wafer surface could be removed by CMP much more efficiently.

# (B) Temporary bonding and wafer thinning

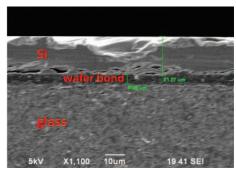

Temporary bonding was achieved through WaferBOND  $^{TM}$  HT-10.10 using SUSS CB6L wafer bonder. The quality of temporary bonding was very important to attain better wafer thinning especially for test chip with 5 $\mu$ m TSVs.

Fig.6 presents the cross-section of  $5\mu m$  temporary bonding, the thickness of WaferBOND<sup>TM</sup> is  $5\mu m$ , and the thickness of the front RDL is  $3\mu m$ . There are no bubble and crack in wafer bond and other interfaces.

Fig.6 Cross-section of 5µm temporary bonding

Based on the good temporary bonding results, the backside wafer grinding/polishing process was applied to expose 5µm Cu TSV backside.

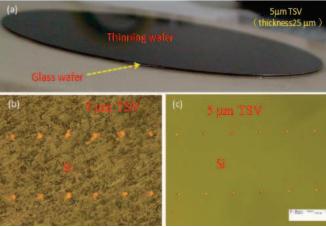

For goal thickness of  $25\mu m$ , silicon wafer with  $5\mu m$  TSVs was grinded down to  $40\mu m$  at high speed of  $0.2\mu m/s$ , and then the wafer with  $40\mu m$  thickness was grinded down to  $30\mu m$  at low speed of  $0.1\mu m/s$ . At that time, polishing was applied to reduce the extra  $5\mu m$  and meanwhile relieve the stress of grinding. Fig.7(a) shows the picture of a temporary bonded silicon wafer with  $5\mu m$  TSVs, which has a thickness of  $25\mu m$ . Fig.7(b) and (c) shows the surface with exposed  $5\mu m$  TSVs after back grinding and polishing.

Fig.7 The surface of back grinding and polishing (a)The picture of a temporary bonded silicon wafer with  $5\mu m$  TSVs (b) The surface after back grinding (c) The surface after back polishing

## (C) Microbump fabrication

After the 5µm Cu TSVs backside were exposed, 200nm  $SiO_2$  passivation layer was deposited through PECVD at the temperature of 200°C. Because the wafer bond can't survival during high temperature, the process temperature after temporary bonding should be controlled under 220°C. Later, the third photolithography was used for defining Ohmic contact area, where  $SiO_2$  passivation layer was etched. The quality of the back RIE process was crucial to electrical testing, and the alignment for opening passivation area of 5µm TSV was very difficult due to the warpage of thinned wafer. Good temporary bonding and enough polishing after wafer thinning would minimize the stress and warpage.

Fig.8 shows the cross-section of  $5\mu m$  TSV daisy chain structure with good TSV filled.

Fig.8 Cross-section of 5µm TSV daisy chain structure

## Fabrication of Interposer with 40µm TSVs

Fig.9 Process flow of Interposer with 40µm TSVs

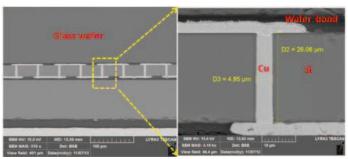

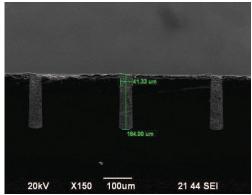

Similar to the fabrication of test chip with 5µm TSVs, via holes of 40µm diameter, 180µm depth TSV interposer was formed by deep RIE and copper electroplating process, as shown in Fig.9. Fig.10 gives SEM image of 40µm TSV filling result. The current density of interposer electroplating was adopted as 1ASD, and the filling rate could achieve 100%.

Fig. 10 SEM image of 40µm TSV filling result

Final wafer thickness was thinned to  $180\mu m$ . For interconnection between  $5\mu m$  TSV chip and Si interposer, Cu/Sn bumps were plated after the deposition of TiW/Cu seed layer.

## **Assembly Process of 3D Integration Testing Vehicle**

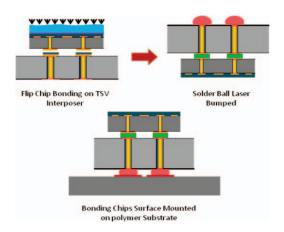

Fig.11 Assembly of 3D Stacking Structure

The assembly process of 3D stacking structure contains two parts shown in Fig.11. Firstly, test chip with 5um TSVs was stacked on TSV interposer by flip-chip bonding. Alignment marks were designed for flip-chip bonding using SUSS FC150 bonder with a higher alignment accuracy and no restricted camera area. Cu/Sn SLID (solid liquid interdiffusion) bonding was adopted as the interconnect method in this bonding process<sup>[5]</sup>.

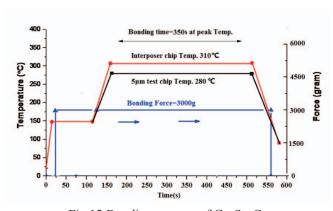

In order to generate enough IMC (Intermetallic Compound) to form reliable metal eutectic bonding, the height of Cu microbump on test chip with 5 $\mu$ m TSVs was designed as 4 $\mu$ m, and the height of Cu/Sn microbump on interposer was 4 $\mu$ m Cu/3 $\mu$ m Sn. The bonding process profile is shown in Fig.12. The whole bonding process was under the protection of Formic acid and N<sub>2</sub> mixture.

Fig.12 Bonding process of Cu-Sn-Cu

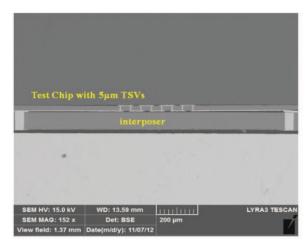

The stacking bonding structure of test chip with  $5\mu m$  TSVs on TSV interposer was shown in Fig.13.

Fig.13 Stacking Bonding of test chip with  $5\mu m$  TSVs on Interposer

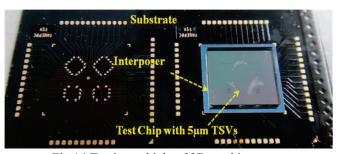

The bonded chips were mounted on organic substrate. Fig.14 shows a finished testing vehicle through solder ball.

Fig.14 Testing vehicle of 3D stacking structure

## Results and discussion

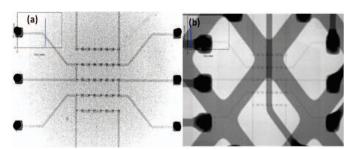

Fig.15 illustrates the X-ray images of the 3D stacking structure. The alignment accuracy of the assembly could be checked from the X-ray images, and the quality of the 3D assembly was also examined through X-ray.

Fig.15 X-ray images of stacked structure (a)Flip chip bonding on TSV Interposer(b) Bonding chips mounted on BT substrate

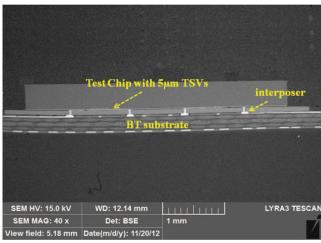

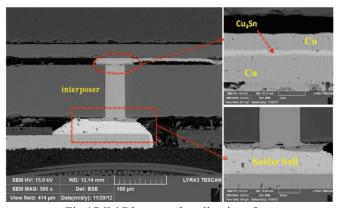

Fig.16 presents the cross-section of 3D integration testing vehicle, which includes test chip with  $5\mu m$  TSVs, interposer with  $40\mu m$  TSVs and organic substrate.

Fig.16 Cross-section of 3D integration testing vehicle

Fig.17 IMC between bonding interface

Fig.17 shows the IMC between bonding interface.  $\text{Cu}_3\text{Sn}$  was generated among the Cu-Sn-Cu bonding interface. The IMC layer between solder ball and Cu pad can be seen clearly from the SEM images.

### **Conclusions**

In this paper, a testing vehicle with test chip and interposer was designed and fabricated. The test chip with  $5\mu m$  TSVs was fabricated, and the key technologies in the fabrication process of  $5\mu m$  TSV were introduced in detail. Robust copper electroplating process for  $5\mu m$  TSVs with high aspect ratio up to 5:1 was realized by the high current density of 0.25ASD. Silicon wafer with  $5\mu m$  TSVs was thinned to  $25\mu m$  based on the good quality of temporary bonding.

The test chip with 5 $\mu$ m TSVs was assembled on the interposer with 40 $\mu$ m TSVs through Cu-Sn-Cu bonding, and the reliable metal eutectic bonding was formed. After that, the bonded module was assembled on designed testing board through solder ball laser bumped and reflow process.

## Acknowledgments

The authors would like to acknowledge the financial support from the National S&T Major Project with No. of 2009ZX02038. The authors would also thank Nano Fabrication Facility of Suzhou Institute of Nano-Tech and Nano-Bionics (SINANO) for the support on process. The authors would like to give special thanks to Shanghai Sinyang Semiconductor Materials Co., Ltd for their tremendous

support of plating chemicals and Dr. Su Wang for valuable discussion.

The authors would also appreciate Ms. Wenyan Yang and Rong Wang from The State Key Laboratory of Tribology, Tsinghua University, for their helps on SEM analysis.

### References

- Tzu Kun Ku, "3D TSV Stacking IC Technologies, Challenges & Opportunities," AMD Technical Forum 2011

- 2. Ming-Jinn Tsai, "Overview of ITRI's TSV Technology," *Trend Micro Titanium Internet Security* 2011

- 3. M. Jürgen Wolf, Thomas Dretschkow. *et al*, "High Aspect Ratio TSV Copper Filling with Different Seed Layers," 2008 Electronic Components and Technology Conference, 2008, pp. 563-569.

- Ziyu Liu, Jian Cai, Qian Wang, Tao Wang, Tiwei Wei, Li Li, "Copper Chemical Mechanical Polishing and Wafer Thinning with Temporary Bonding for Through Silicon Via Interconnect," 2012 International Conference on Electronic Packaging Technology & High Density Packaging, 2012, pp. 488-493

- SUH M-S, KWON H-S, "Growth Kinetics of Cu-Sn Intermetallic Compounds at Interface of 80Sn-20Pb Electrodeposits and Cu Based Leadframe Alloy, and Its Influence on the Fracture Resistance to 90.DEG.-Bending, "Jpn J Appl Phys Part 1, 2000, pp. 6067-6073.

- J.U. Knickerbocker, P.S. Andry, B. Dang, R.R. Horton, C. S. Patel. et al, "3D Silicon Integration," 2008 Electronic Components and Technology Conference, May. 2008, pp. 538-543.

- F. Inoue, T. Yokoyama, S. Tanaka, K. Yamamoto and S. Shingubara, "Addition of PEG-Thiol to Cu Electroless Plating Bath for Realizing Perfect Conformal Deposition in Through-Si Via Holes of 3-D Integration," ECS Transactions, 25 (38) 2010, pp. 31-36.